# EEE/INSTR F313 Analog and Digital VLSI Design

## **Analog VLSI Assignment**

| Name                | ID No.        |

|---------------------|---------------|

| Sashank Krishna S   | 2019A8PS0184P |

| Anirudh Subramanian | 2019A3PS0274P |

| Hariharan Venkat    | 2019A3PS0244P |

## **Problem Number: 82**

### **Acknowledgements**

We would like to extend our deep gratitude to our Lecturers Dr. Anu Gupta and Dr. Samatha Benedict along with our tutorial instructors Dr. Satyendra Kumar Mourya and Dr. Karri Babu Ravi Teja for imparting the knowledge required for the completion of this assignment.

### **Problem Statement:**

#### **Question 82:**

Design a low pass filter with cut-off frequency of 1MHz. Use a CMOS op-amp as shown in the question 77.

- a) Analysis of all equations of your design, with a systematic derivation of all transistors' W/L ratios and simulation of circuits for the following specifications

- i. Open loop gain (DC gain) >= 100dB

- ii. Phase Margin  $\approx 45$  degrees

- iii. Power dissipation <= 1mW

- iv. Slew rate >= 40V/microsecond

- b) Show a biasing circuitry to bias all the voltages in your design (except the input)

- c) Calculate and plot the following parameters for your Op-amp:

- i. DC gain

- ii. Bode Plot for AC gain and Phase

- iii. ICMR plot

- iv. Slew rate

- v. Differential Output voltage swing (dc + Transient)

- vi. Power Consumption

- vii. Input and Output offset voltage

#### **Question 77:**

Design a folded-cascode operational amplifier, in series-shunt feedback, with R-C frequency compensation for the following specifications:

- a) Analysis of all equations of your design, with a systematic derivation of all transistors' W/L ratios and simulation circuit for the following specifications

- i. Voltage gain (closed Loop) >= 50

- ii. -3dB frequency >= 150MHz

- b) Show a biasing circuitry to bias all the voltages in your design (except the input)

- c) Calculate and plot the following parameters for your amplifier:

- i. Slew rate plot for step input of 1V

- ii. DC gain

- iii. Bode plot for AC gain and phase

- iv. ICMR plot

- v. Slew rate

- vi. Output voltage swing differential (dc + transient)

- vii. Power consumption

- viii. Input and output offset voltage

## **Introduction:**

In analog electronics, a low pass filter is a filter that passes signals with a frequency lower than that of cutoff frequency and attenuates signals with frequencies higher than cutoff frequencies. Thus, a low pass filter will essentially 'reject' unwanted high frequencies and accept or pass lower frequencies that the designer of the those circuit requires. only For low frequency applications, Passive low pass filters can be constructed using simple Resistance-Capacitance (RC) circuits, while higher frequencies usually require inductor components. Since such filters have no amplifying elements such as op-amps or transistors, they are usually called *passive filters*.

By combining a basic RC low pass filter with an op-amp, we can construct an Active Low Pass Filter circuit that is simultaneously capable of amplification. In RC Passive first order filter circuits, the amplitude of the output signal is often much less than that of the input signal (i.e., gain<unity), and the load impedance affects the characteristics of the filter, in some cases, causing severe attenuation. To restore this loss of signal, we use *active filters*.

Active Filters contain op-amps/transistors/FETs in the circuit design and use power from external sources to amplify the power at the output signal. Thus, we will be able to create a more selective output response, enabling the output bandwidth of the filter to become narrower or wider. An active filter will generally use an op-amp within its design which usually has a high input impedance, low output impedance and Voltage gain.

## **Design Process:**

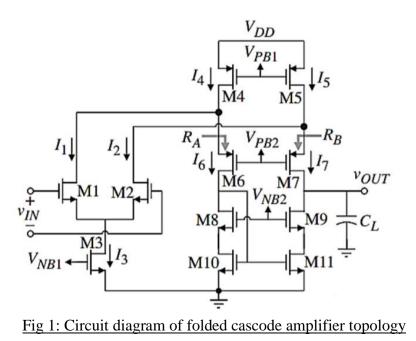

The design process started with the understand of the amplifier topology given to us. In the problem statement for question 82, we are directed to use the amplifier topology elucidated in question 77 which is the folded cascode. We thus started off with research pertaining to this new topology and it's behavior. The circuit diagram we used for this purpose was found in [1] and is shown below.

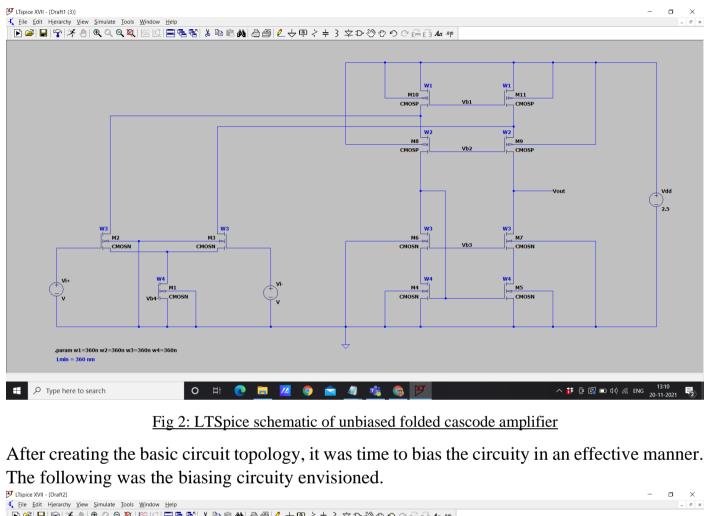

Once this information was gathered, the basic (unbiased) circuit diagram was made on the LTSpice simulation software. A  $V_{DD} = 2.5$  V was taken and the models used for the PMOS and NMOS transistors were taken from the tsmc018.lib file as directed to us by the assignment sheet. The minimum channel length  $L_{min}$  was taken to be 360 nm as given in the assignment problem set. The load capacitor is not included in this schematic.

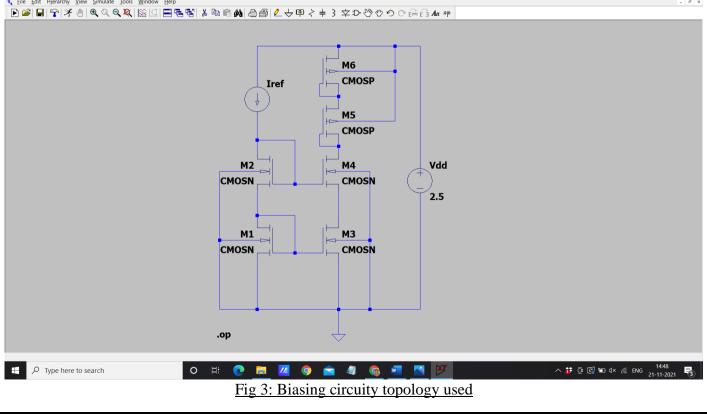

The above topology was chosen after considering the instructions in the assignment which stated the use of a "Single ideal current source of arbitrary value with the positive node tied to  $V_{DD}$  or negative node tied to ground". The above topology has the current source's positive node tied to  $V_{DD}$  and thus satisfies the constraints given in the problem.

The next step was to decide on the value of current we will be using in the biasing circuity. For this purpose, we turned to running simulations on the above topology presented above. We first needed to decide on the potential drops across the P network and the N network. Their sum must be equal to  $V_{DD}$  which is 2.5 V. Due the PMOS being a weaker transistor, we allotted a drop of 1.3 V across the PMOS network and 1.2 V across the NMOS network.

Once this decision was made, simulations had to be run to see the current values which the networks were capable of handling. Since we knew the voltage drop across the network, we were able to parametrically sweep the W values of the transistors while plotting the current flow.

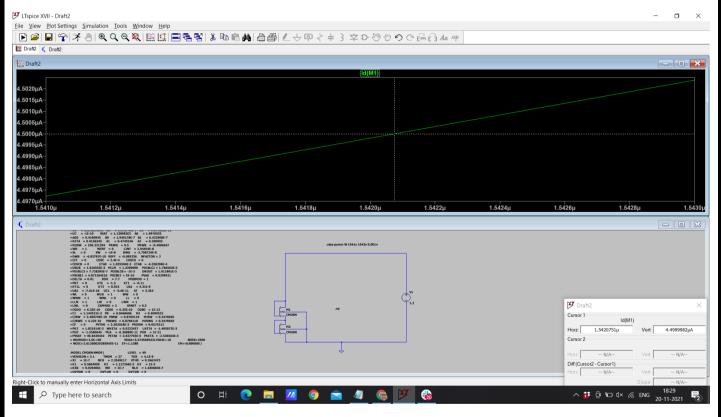

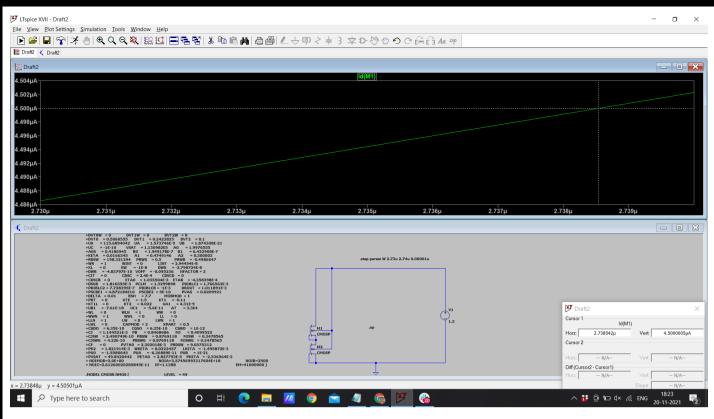

On analyzing the current characteristics, it was decided that a reference current of 4.5  $\mu$ A was prudent. This was the case since very large W values were also not desired. The exact W values for the NMOS and PMOS transistors were found using the simulations.

Fig 4: W value calculation for NMOS network

The thought process was to first create the part of the circuity which we wanted to test. In this case, it was the NMOS network in the biasing circuity. We know the total voltage drop across the network is 1.2 V. Using this information, we connect the circuity and run the simulation. Since we are looking to have 4.5  $\mu$ A of current, we first run a simulation over a large range of W and then keep refining the search till the optimal precise W value is reached. For the NMOS network the W value obtained was Wnmos = 1542.0751 nm. A similar simulation was run for the PMOS network where the drop was 1.3 V (We get Wpmos = 2785.42nm).

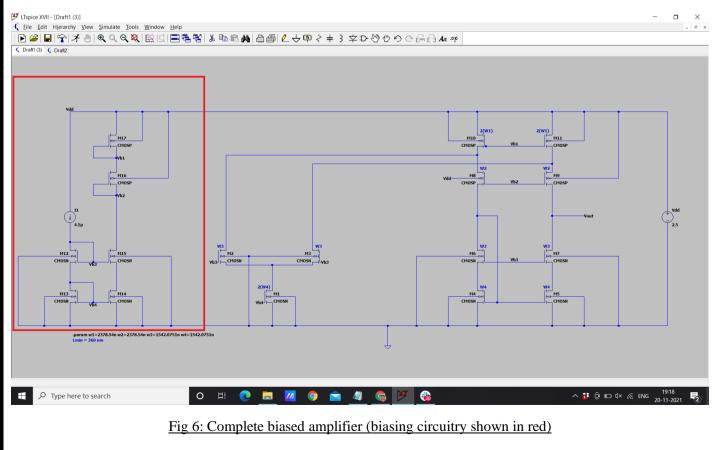

Once the current and width values for the biasing network was created, it was time for us to incorporate the biasing circuity into the amplifier topology. The figure below shows the complete biased amplifier schematic on LTSpice. The W values for all the other transistors in the main amplifier topology were decided with reference to the W values of the biasing network. The factors of '2' were included to allow for the necessary currents to be sinked or sourced at each node.

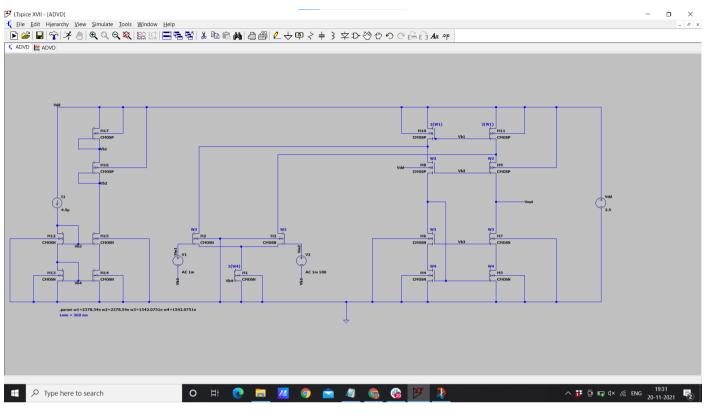

The important question of input bias needs to be addressed at this juncture. Using symmetry as the thumb rule, the input levels were given a DC bias of Vb3 as generated by the biasing circuity (this can be seen in Fig. 6 as well) and the AC small signals were riding on top of the mentioned DC shift. The "modified" AC analysis circuity is shown below.

Fig 7: AC operation of the amplifier

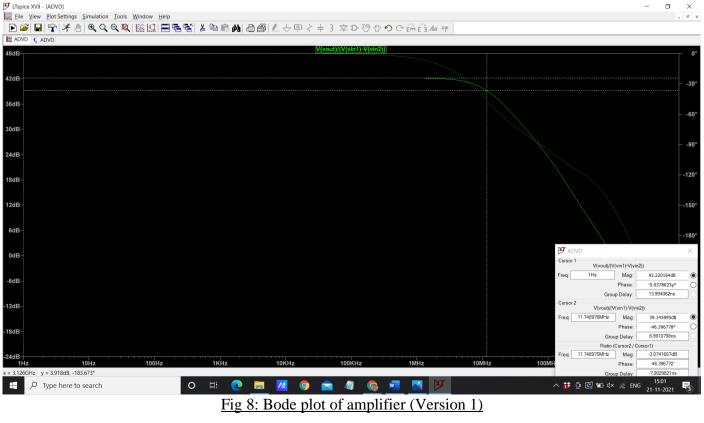

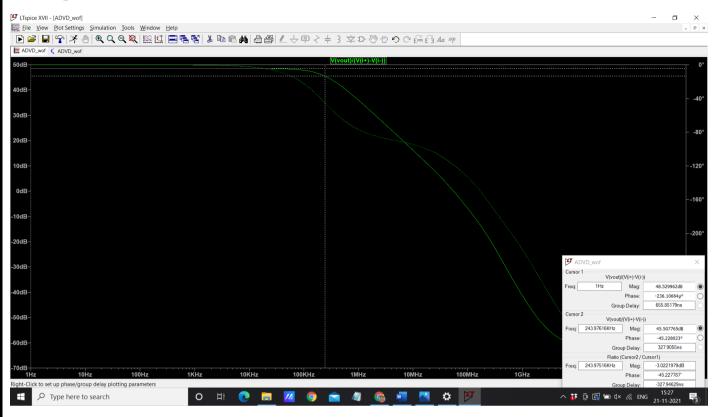

Now that the circuitry was AC operation ready, it was time to test the frequency response of the amplifier we had created. The Bode plot generated for the Version 1 open loop amplifier is shown below.

From the Bode plot, we see that we are getting around 42 dB of low frequency gain with a bandwidth of around 11 MHz. Before we move further, it is important for us to add in the load capacitance  $C_L$ . For reasons explained later, the  $C_L$  value was taken to be 150 fF which adheres to the >100 fF constraint imposed in the problem. The modified Bode plot after adding in the load capacitance is shown below.

Fig 9: Bode plot after load capacitance of 150 fF was added at output

To our dismay, we notice the extremely poor bandwidth here of around 243 kHz which is much lower than the required value of 1 MHz. As a result, it is now time to implement the feedback and also incorporate frequency compensation to allow for a better frequency response.

It is important to note that the final circuit must be a feedback enabled low pass filter with a cutoff frequency of 1 MHz. While Problem 82 directs us to problem 77 for amplifier specifications, we note that the topology of the folded cascode is the most salient among those given specifications and try to optimize for the final goal at every stage.

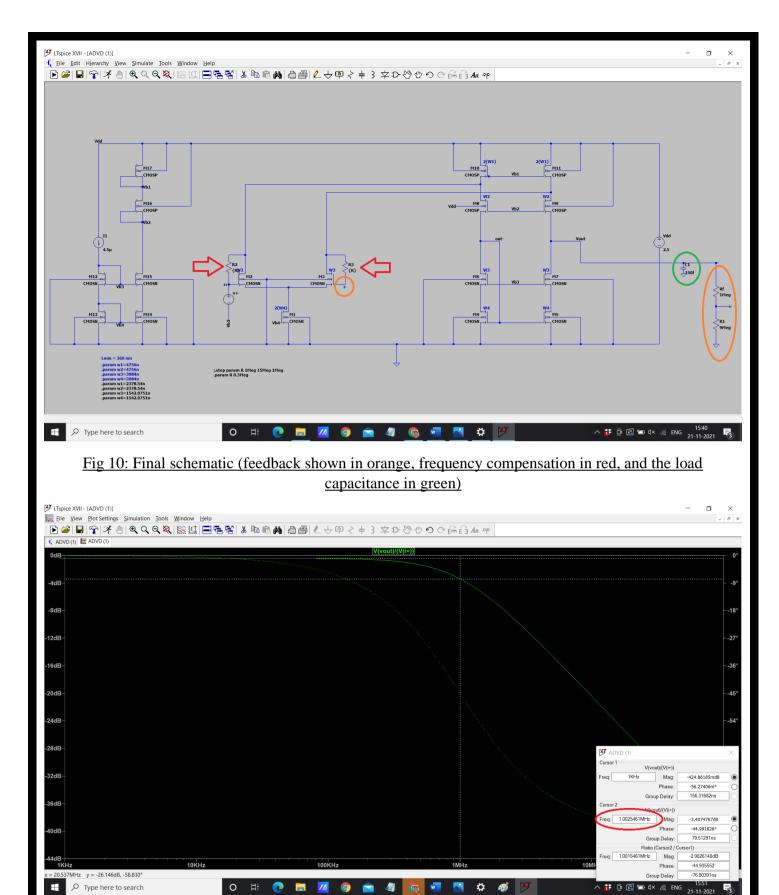

As directed to us in the question, series-shunt feedback was incorporated using a resistive divider. Additionally, attempts were made to insert a "zero" into the frequency response of the amplifier, thereby increasing our bandwidth. The resistive components used for this purpose, along with the load capacitance  $C_L$  go hand in hand and need to be tweaked carefully.

The final proposed schematic for the low pass filter, along with the Bode plot is showcased below. The diagrams are followed by the elaboration of the deliberations leading upto this schematic.

Fig 11: Bode plot of final low pass filter. -3dB cutoff frequency highlighted in red

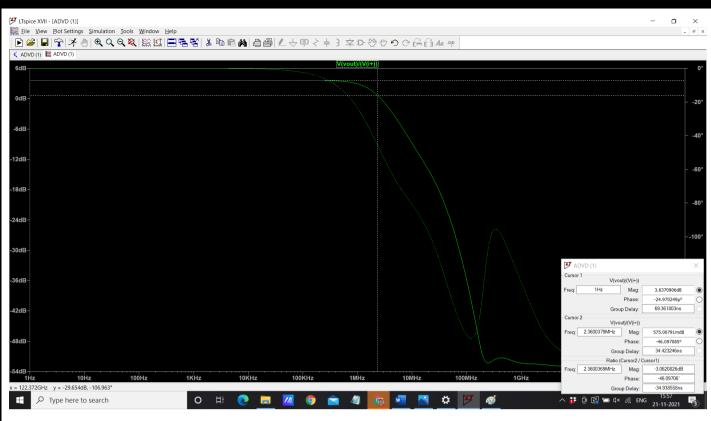

After careful deliberation, the value of R in the frequency compensation was chosen to be 300 k $\Omega$ . The thought process here is as follows. We can alter the bandwidth by changing the resistance and capacitance values. Increasing the resistance value allows for an increase in bandwidth. For example, a case where  $R = 1M\Omega$  is shown below. The bandwidth for this case is almost double of the proposed solution.

Fig 12: Showing the increase in bandwidth for a higher R value  $(1M\Omega)$

At the same time, as VLSI engineers, it is our duty to account for the Silicon areas. Having very high resistance nodes will imply more silicon area and will thus increase the costs. The value of 0.3 M $\Omega$  used in our proposed solution takes this into account and tries to use the minimum resistance while still meeting the minimum cutoff frequency requirement of 1 MHz.

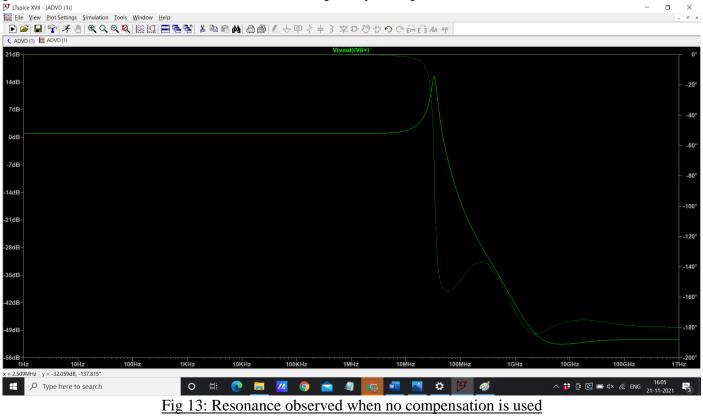

One \interesting case we came across during our design process was the frequency response where we witnessed resonance firsthand before implementing frequency compensation. This problem is solved when the resistor for frequency compensation was added.

## **Final specification documentations:**

#### <u>V<sub>DD</sub> = 2.5 Volts</u>

Simulations were run at 3 different temperatures of 0, 27 and 100°C. The results are tabulated below.

| <b>Property</b>               | <u>0°C</u> | <u>27°C</u> | <u>100°C</u> |

|-------------------------------|------------|-------------|--------------|

| Cutoff Frequency (MHz)        | 1.005      | 1.006       | 1.03         |

| Power Dissipation ( $\mu W$ ) | 57.4866    | 56.8045     | 55.1318      |

| DC gain (mdB)                 | -411.6981  | -424.8581   | -498.2211    |

| Input DC bias (V)             | 1.22589    | 1.23207     | 1.25513      |

| ICMR (V)                      | 2.07       | 2.07        | 2.07         |

#### W/L Table (NMOS – green, PMOS – orange):

| Transistor No. | <u>W (nm)</u> | <u>L (nm)</u> | W/L    |

|----------------|---------------|---------------|--------|

| M1             | 3084.1502     | 360           | 8.567  |

| M2             | 1542.0751     | 360           | 4.284  |

| M3             | 1542.0751     | 360           | 4.284  |

| M4             | 1542.0751     | 360           | 4.284  |

| M5             | 1542.0751     | 360           | 4.284  |

| M6             | 1542.0751     | 360           | 4.284  |

| M7             | 1542.0751     | 360           | 4.284  |

| M8             | 2378.54       | 360           | 6.607  |

| M9             | 2378.54       | 360           | 6.607  |

| M10            | 4757.08       | 360           | 13.214 |

| M11            | 4757.08       | 360           | 13.214 |

| M12            | 1542.0751     | 360           | 4.284  |

| M13            | 1542.0751     | 360           | 4.284  |

| M14            | 1542.0751     | 360           | 4.284  |

| M15            | 1542.0751     | 360           | 4.284  |

| M16            | 4757.08       | 360           | 13.214 |

| M17            | 2378.54       | 360           | 6.607  |

#### Voltages at all nodes:

| 0         | perating Point |         |  |

|-----------|----------------|---------|--|

| V(n003):  | 0.560559       | voltage |  |

| V(vb4):   | 0.548278       | voltage |  |

| V(n005):  | 0.189182       | voltage |  |

| V(out-):  | 0.189183       | voltage |  |

| V(n006) : | 0.819738       | voltage |  |

| V(vb3):   | 1.23207        | voltage |  |

| V(vout):  | 1.24929        | voltage |  |

| V (vdd) : | 2.5            | voltage |  |

| V(vb1):   | 1.94658        | voltage |  |

| V(n001):  | 1.62424        | voltage |  |

| V(vb2):   | 1.19369        | voltage |  |

| V(n002):  | 1.29241        | voltage |  |

| V(i−):    | 1.2504         | voltage |  |

| V(i+):    | 1.23207        | voltage |  |

| V(n004):  | 0.547935       | voltage |  |

| V(nc 01): | 1.23207        | voltage |  |

#### V<sub>DD</sub> variation

The assignment instructed us to run the simulations at 10% higher and lower of  $V_{DD}$  with 0 degrees Celsius at 10% lower and 100 degrees Celsius at 10% higher. The results are tabulated below.

| <b><u>Property</u></b>        | <u>VDD = 2.25 V, T = <math>0^{\circ}</math>C</u> | <u>VDD = 2.75 V, T = <math>100^{\circ}C</math></u> |

|-------------------------------|--------------------------------------------------|----------------------------------------------------|

| Cutoff Frequency (MHz)        | 1.378                                            | 1.002                                              |

| Power Dissipation ( $\mu W$ ) | 48.2                                             | 63.997898                                          |

| DC gain (mdB)                 | -293.47365                                       | -467.11457                                         |

| Input DC bias (V)             | 1.217                                            | 1.263                                              |

### **References:**

- 1. https://aip.scitation.org/doi/pdf/10.1063/1.5142133

- 2. <u>https://www.electronicspoint.com/forums/resources/managing-temperature-in-ltspice.18/</u>

- 3. <u>https://www.youtube.com/watch?v=y31UMhCaTsY</u>

- 4. <u>https://www.youtube.com/watch?v=FxbnTWx8UZ0&t=4750s</u>